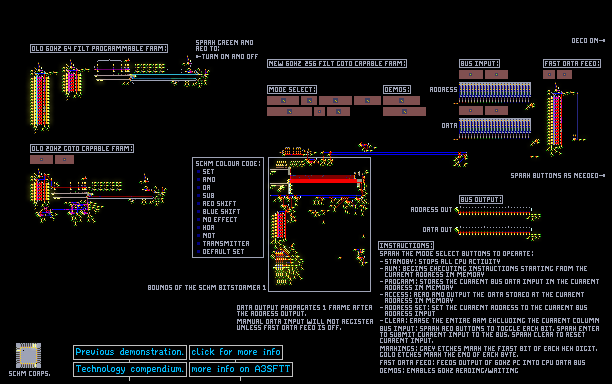

SCHM BitStormer 1 Preview by Schmolendevice

The future of TPT computing is on its way! This save features a 256 FILT particle 768 byte FRAM capable of read and write access 60 times a second! This device is the precursor to my 60 Hz BitStormer CPU. 8/12/15 User I/O interface finished.

computer

electronics

processor

60hz

conv

subframe

howitworks

a3sftt

Comments

-

Schmolendevice 27th Oct 2016

10/27/16 SCHM Trademark update.

10/27/16 SCHM Trademark update. -

Schmolendevice 18th Aug 2015

Yeah, but indeed I do have ambitions to make a powerful 60 Hz processor for high speed vector operations. I'd have to look into the circuitry for high speed multiplication and integer division eventually. I'm still trying to improve my adders and counters though.

Yeah, but indeed I do have ambitions to make a powerful 60 Hz processor for high speed vector operations. I'd have to look into the circuitry for high speed multiplication and integer division eventually. I'm still trying to improve my adders and counters though. -

unknownkarma 17th Aug 2015

Oh, and I already saw the addition, was what got me to ask that question

Oh, and I already saw the addition, was what got me to ask that question -

unknownkarma 17th Aug 2015

Damn, I had an idea for a graphics card that could process polygons but it would require subframe division to be useful, otherwise you might as well just program the frames into the program

Damn, I had an idea for a graphics card that could process polygons but it would require subframe division to be useful, otherwise you might as well just program the frames into the program -

Schmolendevice 17th Aug 2015

No, but I do have a 60 Hz 16 bit adder design. The problem with it is that operands during a frame are loaded from the top and the result propagated downwards. At the bottom of the adder, ARAY shoots upwards producing a retreivable answer/BRAY ctype at the top available during the next frame. I would prefer that the result be immediately accessible at the bottom or side of the adder in the same frame so I may have more space for flag update processing.

No, but I do have a 60 Hz 16 bit adder design. The problem with it is that operands during a frame are loaded from the top and the result propagated downwards. At the bottom of the adder, ARAY shoots upwards producing a retreivable answer/BRAY ctype at the top available during the next frame. I would prefer that the result be immediately accessible at the bottom or side of the adder in the same frame so I may have more space for flag update processing. -

unknownkarma 17th Aug 2015

Have you managed to create subframe division?

Have you managed to create subframe division? -

AwesomeBroTy 16th Aug 2015

This is the most amazing thing in the universe +42

This is the most amazing thing in the universe +42 -

mecha-man 15th Aug 2015

Sorry, I misread excluding as including.

Sorry, I misread excluding as including. -

mecha-man 14th Aug 2015

If it is running CLEAR doesn't clear the current column, if it is in standby CLEAR doesn't clear the current address.

If it is running CLEAR doesn't clear the current column, if it is in standby CLEAR doesn't clear the current address. -

2015 13th Aug 2015

impresive +1

impresive +1