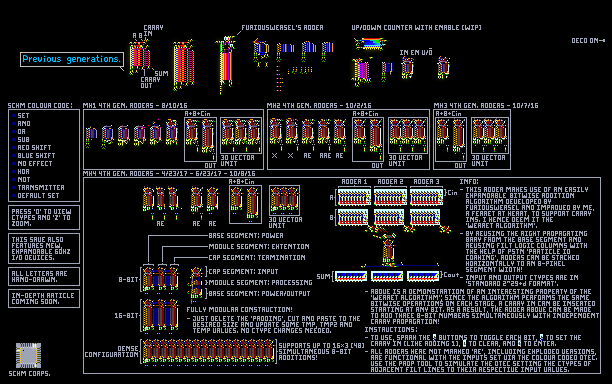

A3SFTT 60 Hz Components 2 by Schmolendevice

Started 6/17/16. Breakthrough design completed 8/10/16. 8/15/16 Published adder designs. 10/2/16 Mk2 version with bit retention completed. 10/7/16 Mk3 complete. 3/2/17 Mk4 complete! 10/8/17 Final release, finally! Description in save.

60hz

subframe

electronic

electronics

adder

math

processing

components

counter

Comments

-

QuanTech 30th Aug 2016

yeeep...

yeeep... -

TNTPig1 30th Aug 2016

nah i faved this save a while back XD

nah i faved this save a while back XD -

TNTPig1 30th Aug 2016

i can see cuz i have hackz lol

i can see cuz i have hackz lol -

TNTPig1 30th Aug 2016

why did this go private?????

why did this go private????? -

Schmolendevice 19th Aug 2016

@Nean Oh no. That was just some descriptions of the _possibilities_ for how small processors could be made. This is just the current smallest binary adder only capable of binary addition of 8 or 16-bit integers. No FILT-RAM or instruction decoder here.

@Nean Oh no. That was just some descriptions of the _possibilities_ for how small processors could be made. This is just the current smallest binary adder only capable of binary addition of 8 or 16-bit integers. No FILT-RAM or instruction decoder here. -

Nean 19th Aug 2016

So, is this a fully contained computer? It just has one instruction?

So, is this a fully contained computer? It just has one instruction? -

QuanTech 18th Aug 2016

"It's a ferret."

"It's a ferret." -

QuanTech 17th Aug 2016

wow! a computer that only has 1 instruction!!!

wow! a computer that only has 1 instruction!!! -

Schmolendevice 17th Aug 2016

One Instruction Set Computer. Wikipedia will explain it better. Can compute anything but only with one instruction. It may not even need anything the size of an adder.

One Instruction Set Computer. Wikipedia will explain it better. Can compute anything but only with one instruction. It may not even need anything the size of an adder. -

QuanTech 17th Aug 2016

what's an OISC?

what's an OISC?