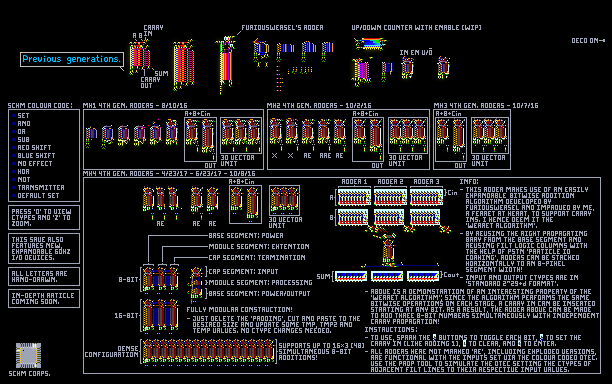

A3SFTT 60 Hz Components 2 by Schmolendevice

Started 6/17/16. Breakthrough design completed 8/10/16. 8/15/16 Published adder designs. 10/2/16 Mk2 version with bit retention completed. 10/7/16 Mk3 complete. 3/2/17 Mk4 complete! 10/8/17 Final release, finally! Description in save.

60hz

subframe

electronic

electronics

adder

math

processing

components

counter

Comments

-

Schmolendevice 1st Oct 2016

@QuanTech Yeah, I've seen that mark2222 has been back. I didn't see his activity until recently.

@QuanTech Yeah, I've seen that mark2222 has been back. I didn't see his activity until recently. -

QuanTech 29th Sep 2016

MAEK A GPU!!!! jk

MAEK A GPU!!!! jk -

QuanTech 9th Sep 2016

@Schmolendevice ok got it. tnks!

@Schmolendevice ok got it. tnks! -

Schmolendevice 3rd Sep 2016

@QuanTech I mentioned bit retention in one of our PMs on FILT technology. It's essentially deciding the use and preservation of the upper three "red" bits during XOR, AND and shift operations in order to still be able to represent the number "zero" without the ctype cancelling out, stopping the BRAY beam from any further calculation. Hence what I call "2^29+d" format where 536,870,912 is the equivalent of "zero."

@QuanTech I mentioned bit retention in one of our PMs on FILT technology. It's essentially deciding the use and preservation of the upper three "red" bits during XOR, AND and shift operations in order to still be able to represent the number "zero" without the ctype cancelling out, stopping the BRAY beam from any further calculation. Hence what I call "2^29+d" format where 536,870,912 is the equivalent of "zero." -

QuanTech 1st Sep 2016

also, when can i expect your processor to be completed? i'm really excited to see the size of it!

also, when can i expect your processor to be completed? i'm really excited to see the size of it! -

QuanTech 1st Sep 2016

also, when can i expect your processor to be completed? i'm really excited to see the size of it!

also, when can i expect your processor to be completed? i'm really excited to see the size of it! -

QuanTech 1st Sep 2016

what is bit retention?

what is bit retention? -

Schmolendevice 31st Aug 2016

@QuanTech That's just the intermediate side effects of the development process. I'm essentially just fleshing out the most efficient power distribution layout for the counter as well as managing bit retention.

@QuanTech That's just the intermediate side effects of the development process. I'm essentially just fleshing out the most efficient power distribution layout for the counter as well as managing bit retention. -

QuanTech 31st Aug 2016

oohhh, somethin malfunctioned there... shooting bray in 4 different directions...

oohhh, somethin malfunctioned there... shooting bray in 4 different directions... -

Schmolendevice 30th Aug 2016

@TNTPig1 Oh, more like it was originally private until the subframe hype some weeks ago whereby I've now resumed development on an up/down binary counter - 4th generation model.

@TNTPig1 Oh, more like it was originally private until the subframe hype some weeks ago whereby I've now resumed development on an up/down binary counter - 4th generation model.