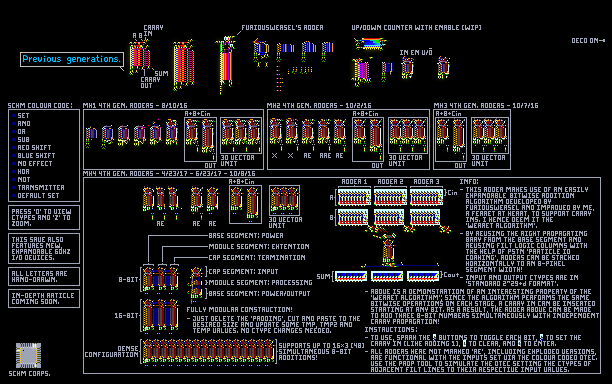

A3SFTT 60 Hz Components 2 by Schmolendevice

Started 6/17/16. Breakthrough design completed 8/10/16. 8/15/16 Published adder designs. 10/2/16 Mk2 version with bit retention completed. 10/7/16 Mk3 complete. 3/2/17 Mk4 complete! 10/8/17 Final release, finally! Description in save.

60hz

subframe

electronic

electronics

adder

math

processing

components

counter

Comments

-

NoVIcE 14th Oct 2017

MultiCore GPU is already done i think, by mark2222.

MultiCore GPU is already done i think, by mark2222. -

QuanTech 12th Oct 2017

@NoVIcE can't wait for floating-point hardware!! :D And then multi-core 'GPU's

@NoVIcE can't wait for floating-point hardware!! :D And then multi-core 'GPU's -

NoVIcE 12th Oct 2017

Great, they are small AND subframe. If we could make a real small 60 clock cycles computer, it would be very cool.

Great, they are small AND subframe. If we could make a real small 60 clock cycles computer, it would be very cool. -

QuanTech 10th Oct 2017

yay! I've been checking this save like everyday

yay! I've been checking this save like everyday -

Cool4Cool 10th Oct 2017

Can't wait for moar stuff!

Can't wait for moar stuff! -

Schmolendevice 9th Oct 2017

10/8/17 Presently caught up in my second co-op workterm. Now with mark2222's decimal multiplier out there, I have finally released this months-due save with demo and description.

10/8/17 Presently caught up in my second co-op workterm. Now with mark2222's decimal multiplier out there, I have finally released this months-due save with demo and description. -

Schmolendevice 2nd Jul 2017

7/2/17 Demo interface to 3-in-1 adder finished. Working on final presentation.

7/2/17 Demo interface to 3-in-1 adder finished. Working on final presentation. -

QuanTech 26th Jun 2017

Ah yisssssss some updates

Ah yisssssss some updates -

Schmolendevice 24th Jun 2017

6/23/17 4th Generation Mk4 Adder finalized and purged of unnecessary DMND layering. Now in final form factor. :D I/O demonstration underway.

6/23/17 4th Generation Mk4 Adder finalized and purged of unnecessary DMND layering. Now in final form factor. :D I/O demonstration underway. -

Schmolendevice 23rd Jun 2017

6/23/17 Started implementing CONV updates; removing unneeded DMND layering.

6/23/17 Started implementing CONV updates; removing unneeded DMND layering.