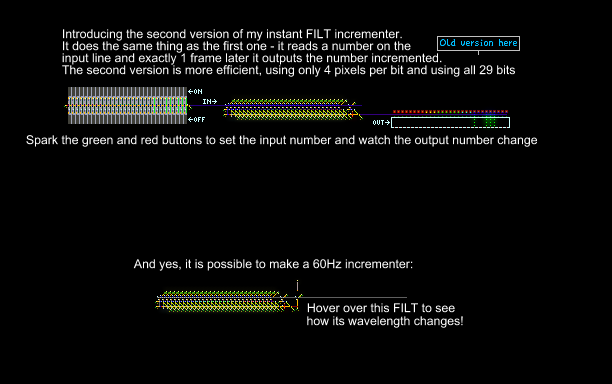

Instant incrementer V2! by mniip

I've reviewed the previous design, which appeared to be totally inefficient, and made this. Also features a 1-per-frame counter setup.

data

transfer

sprk

60hz

subframe

electronics

filt

Comments

-

thespazz 11th Jan 2015

neet. nice that it dosnt use wifi. :P @the_new_powder99999: they can whitch is weird. i had a small electronic that used btry-conv but it dosnt work anymore. and if there was a version that didnt use conv or btry then it would have to use wifi. it it would be too large to use.

neet. nice that it dosnt use wifi. :P @the_new_powder99999: they can whitch is weird. i had a small electronic that used btry-conv but it dosnt work anymore. and if there was a version that didnt use conv or btry then it would have to use wifi. it it would be too large to use. -

the_new_powder99999 11th Jan 2015

A version that doesn't use conv+btry would be good, conv+btry machines can stop working for strange reasons.

A version that doesn't use conv+btry would be good, conv+btry machines can stop working for strange reasons. -

Schmolendevice 11th Jan 2015

Just a question, is some of the ARAY you are using just a quicker to format alternative to FILT with tmp = 6? Plus what are the seemingly extra ARAY and CRAY littered (identically) throughout the circuit for? Some DTEC around those 'white' XORs don't seem to really be doing much; well after seeing that it actually is essential I'd guess there's a number of sub-frame things happening. Still have to figure out how you set this up.

Just a question, is some of the ARAY you are using just a quicker to format alternative to FILT with tmp = 6? Plus what are the seemingly extra ARAY and CRAY littered (identically) throughout the circuit for? Some DTEC around those 'white' XORs don't seem to really be doing much; well after seeing that it actually is essential I'd guess there's a number of sub-frame things happening. Still have to figure out how you set this up. -

Schmolendevice 11th Jan 2015

Plus, as per the CPU designs I have in mind that the preferrable format would be 'tower like' or verticle so the components are thin and fit side by side in the core (e.g. PC > Instruction Cache, decoder below, L1 cache, registers, ALU devices). All towards achieving multi-core TPT computing.

Plus, as per the CPU designs I have in mind that the preferrable format would be 'tower like' or verticle so the components are thin and fit side by side in the core (e.g. PC > Instruction Cache, decoder below, L1 cache, registers, ALU devices). All towards achieving multi-core TPT computing. -

Schmolendevice 11th Jan 2015

Aaach, mozt glorhiouz 60 Hz binary incrementation ist achieved. Sigh, well wonderful very much. Next step in terms of compact, high speed TPT computing is to allow it to be accessed asynchronously with arbitrary count enables as well as support for goto operations (resetting the current PC contents to a new address).

Aaach, mozt glorhiouz 60 Hz binary incrementation ist achieved. Sigh, well wonderful very much. Next step in terms of compact, high speed TPT computing is to allow it to be accessed asynchronously with arbitrary count enables as well as support for goto operations (resetting the current PC contents to a new address). -

GalacticCat 11th Jan 2015

i did not know the utility but is ingenious, hehe +1

i did not know the utility but is ingenious, hehe +1