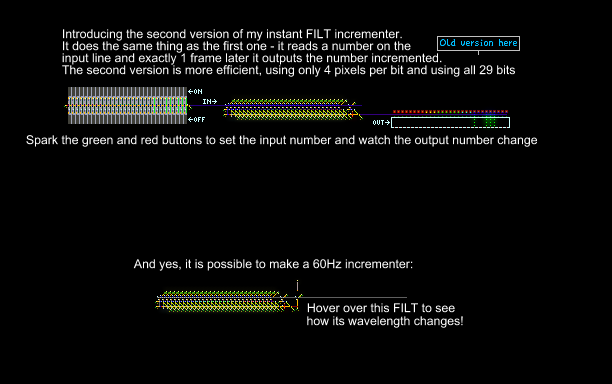

Instant incrementer V2! by mniip

I've reviewed the previous design, which appeared to be totally inefficient, and made this. Also features a 1-per-frame counter setup.

data

transfer

sprk

60hz

subframe

electronics

filt

Comments

-

Schmolendevice 13th Jan 2015

Sigh, well my counter is getting rather messed up due to some strange timing issues and things just not working. Supposedly if you have an ARAY, FILT and DTEC on the same row, left to right, the order of operations is fire ARAY, propagate through FILT, DTEC scans surroundings. On the row below a BRAY should appear but when scanning that area is cleared.

Sigh, well my counter is getting rather messed up due to some strange timing issues and things just not working. Supposedly if you have an ARAY, FILT and DTEC on the same row, left to right, the order of operations is fire ARAY, propagate through FILT, DTEC scans surroundings. On the row below a BRAY should appear but when scanning that area is cleared. -

mniip 13th Jan 2015

@mecha-man Oh, pmap tricks, I haven't considered that before. Thanks for the idea! I've come up with a nice compact ARAY design: 1713452

@mecha-man Oh, pmap tricks, I haven't considered that before. Thanks for the idea! I've come up with a nice compact ARAY design: 1713452 -

mecha-man 12th Jan 2015

@mniip: Using layering you can put DMND on top of the ARAY, this would cause it not to be affected by the CONV, you can even put the BTRY on top of the CONV and then stick a DMND on top of that.

@mniip: Using layering you can put DMND on top of the ARAY, this would cause it not to be affected by the CONV, you can even put the BTRY on top of the CONV and then stick a DMND on top of that. -

Schmolendevice 12th Jan 2015

Here's some unfinished stuff I've been working on. ID:1713171. Perhaps some technology convention or powder IEEE to bring the 'high speed sub-framers' together?

Here's some unfinished stuff I've been working on. ID:1713171. Perhaps some technology convention or powder IEEE to bring the 'high speed sub-framers' together? -

Garuda 12th Jan 2015

Ok, i dont understand, how did you come up with this idea in the first place? like did you just think of it when you were on the computer or walking about, or was it an accidental kind of thing?

Ok, i dont understand, how did you come up with this idea in the first place? like did you just think of it when you were on the computer or walking about, or was it an accidental kind of thing? -

mniip 12th Jan 2015

@mecha-man Layering won't help much. CONV has to be only adjacent to METL, and ARAY has to be placed before CONV, so that already defines the ^-shape. then there's the fact that the bottom of this construction cannot touch the input line, so you have to lift it by 1px, and add an ARAY in between, and at that point, you already cannot place these thing at every 4px.

@mecha-man Layering won't help much. CONV has to be only adjacent to METL, and ARAY has to be placed before CONV, so that already defines the ^-shape. then there's the fact that the bottom of this construction cannot touch the input line, so you have to lift it by 1px, and add an ARAY in between, and at that point, you already cannot place these thing at every 4px. -

Schmolendevice 12th Jan 2015

Well I didn't have to use layering for mine. Just once again that I have to deliver some constant spark INST + ARAY into the circuit from the left which makes it technically of a similar thickness to this design but 3 bits per pixel. I use sort of a basic half adder logic and sub frame ripple.

Well I didn't have to use layering for mine. Just once again that I have to deliver some constant spark INST + ARAY into the circuit from the left which makes it technically of a similar thickness to this design but 3 bits per pixel. I use sort of a basic half adder logic and sub frame ripple. -

Garuda 12th Jan 2015

Yes, your full profile picture just looks familiar.

Yes, your full profile picture just looks familiar. -

mecha-man 12th Jan 2015

There's one word that can solve all your problems, layering.

There's one word that can solve all your problems, layering. -

mniip 12th Jan 2015

@choruseye It's a red summation symbol (capital greek sigma) overlayed over a blue integral symbol. Or do you mean my avatar seems familiar to you as a whole?

@choruseye It's a red summation symbol (capital greek sigma) overlayed over a blue integral symbol. Or do you mean my avatar seems familiar to you as a whole?