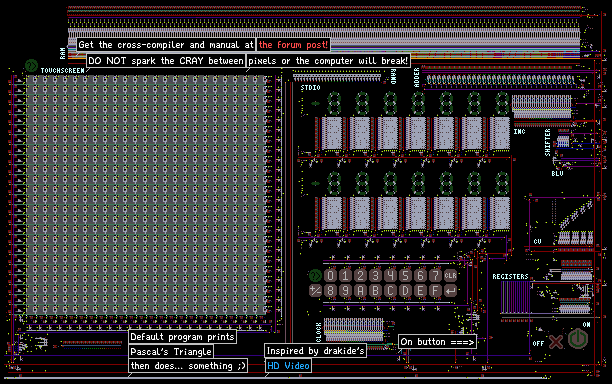

LightPC (0.6 Hz computer) by mark2222

A 0.6 Hz full-fledged WiFi-less 29-bit computer based on photon technology. Rather fast. WARNING: May lag. Note: The first part of the default program does not require input. Press the On button and LightPC will print Pascal's Triangle automatically.

light

filt

rllytouch

photon

screen

29bit

touchscreen

computer

processor

electronics

Comments

-

QuanTech 20th Jul 2016

+MEOWS filt has different tmp modes. For example, filt with tmp of 1 is in the AND mode. In AND mode, the filt performs the AND operation on all the bits in the filt and photon/BRAY spectrum. Sorry for the terrible explanation xD

+MEOWS filt has different tmp modes. For example, filt with tmp of 1 is in the AND mode. In AND mode, the filt performs the AND operation on all the bits in the filt and photon/BRAY spectrum. Sorry for the terrible explanation xD -

MEOWS 17th Jul 2016

how do the logic gate filts work?

how do the logic gate filts work? -

LaRoso 12th Mar 2016

wow! that thing is very slow, but very epic +1

wow! that thing is very slow, but very epic +1 -

erictom333 15th Nov 2015

my compiler 1885897 48 instructions

my compiler 1885897 48 instructions -

erictom333 12th Nov 2015

can you make a tpt compiler?

can you make a tpt compiler? -

I_Always_no_scoping 24th Aug 2015

hi jacob

hi jacob -

jacob1 23rd Aug 2015

mooooo

mooooo -

benrox 27th May 2015

yeash your other computer is so famous but youve had this fantastic one al along and i only just found out and ive made a computer in minecraft whats the method to doing these trigangles id like to do the same for mine

yeash your other computer is so famous but youve had this fantastic one al along and i only just found out and ive made a computer in minecraft whats the method to doing these trigangles id like to do the same for mine -

lostkagamine 13th May 2015

Can it run Minecraft? That's the big question.

Can it run Minecraft? That's the big question. -

tjitte 2nd Mar 2015

this is amazing. can you make a minimal version, so it runs faster on slow computers? I'm in love

this is amazing. can you make a minimal version, so it runs faster on slow computers? I'm in love