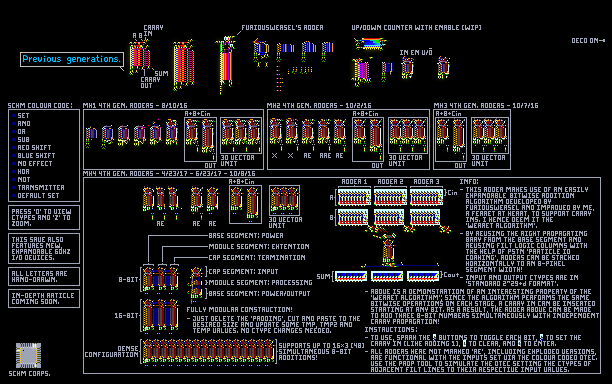

A3SFTT 60 Hz Components 2 by Schmolendevice

Started 6/17/16. Breakthrough design completed 8/10/16. 8/15/16 Published adder designs. 10/2/16 Mk2 version with bit retention completed. 10/7/16 Mk3 complete. 3/2/17 Mk4 complete! 10/8/17 Final release, finally! Description in save.

60hz

subframe

electronic

electronics

adder

math

processing

components

counter

Comments

-

Schmolendevice 5th May 2017

5/4/17 Maybe. I might learn stuff in my current VHDL course. Otherwise, I'll be sticking to standard "bitwise analysis" and Boolean simplifications. I am planning on writing up an "FDL" (FILT description) that may or may not support direct "FILT logic synthesis".

5/4/17 Maybe. I might learn stuff in my current VHDL course. Otherwise, I'll be sticking to standard "bitwise analysis" and Boolean simplifications. I am planning on writing up an "FDL" (FILT description) that may or may not support direct "FILT logic synthesis". -

QuanTech 3rd May 2017

i wonder if you could use an optimization algorithm to make insanely compact and efficient subframe stuff

i wonder if you could use an optimization algorithm to make insanely compact and efficient subframe stuff -

Schmolendevice 5th Mar 2017

3/4/17 Thinking more about it, but not having officially tested it, the number of "stages" in the adder merely limits the longest carry ripple that can occur, yet that ripple can start "anywhere" in the ctype. That is, for something the size of an 8-bit adder, you can already fit three, independent 8-bit additions with unique carry outs into their ctype. Three adders for the chip area of one; something I had hoped of my concept of "P-SOT" "light transistors".

3/4/17 Thinking more about it, but not having officially tested it, the number of "stages" in the adder merely limits the longest carry ripple that can occur, yet that ripple can start "anywhere" in the ctype. That is, for something the size of an 8-bit adder, you can already fit three, independent 8-bit additions with unique carry outs into their ctype. Three adders for the chip area of one; something I had hoped of my concept of "P-SOT" "light transistors". -

QuanTech 4th Mar 2017

@Schmolendevice woah! Accidents are (sometimes) cool

@Schmolendevice woah! Accidents are (sometimes) cool -

Schmolendevice 3rd Mar 2017

3/3/17 E.g. Have a 27-bit adder that can be configured internally as a 16-bit adder, a 16-bit and 8-bit adder, three 8-bit adders, 5 4-bit adders or any combination thereof. Another fascinating prospect is to see if this arbitrary carry "insertion" might permit BCD addition or operations of any other radix.

3/3/17 E.g. Have a 27-bit adder that can be configured internally as a 16-bit adder, a 16-bit and 8-bit adder, three 8-bit adders, 5 4-bit adders or any combination thereof. Another fascinating prospect is to see if this arbitrary carry "insertion" might permit BCD addition or operations of any other radix. -

Schmolendevice 3rd Mar 2017

3/3/17 And apparently, using the Cin ctype, you can apply/start a carry in at any bit, but this won't let you add three numbers or "double carry" anywhere. Perhaps the "extra bit" will allow me to dynamically split the adder in half and perform two or more separate additions on the same component; oh goodness, serendipity. :D

3/3/17 And apparently, using the Cin ctype, you can apply/start a carry in at any bit, but this won't let you add three numbers or "double carry" anywhere. Perhaps the "extra bit" will allow me to dynamically split the adder in half and perform two or more separate additions on the same component; oh goodness, serendipity. :D -

Schmolendevice 3rd Mar 2017

3/3/17 I'm concerned that my 8-bit adders might actually be 9-bit adders and have to be shortened by a pixel. Just a touch inconvenient. I will have to investigate its capabilities.

3/3/17 I'm concerned that my 8-bit adders might actually be 9-bit adders and have to be shortened by a pixel. Just a touch inconvenient. I will have to investigate its capabilities. -

QuanTech 3rd Mar 2017

Awesome! Nice to see that progress is continuing! TPT users are headed for some surprises

Awesome! Nice to see that progress is continuing! TPT users are headed for some surprises -

Schmolendevice 2nd Mar 2017

3/2/17 The Mk4 4th generation adder has been completed (in cleanup phase)! As you can see, I've set up 16 of the buggers side by side; they could be easily used in an SIMD setup of the scale of mark2222's GPU. Otherwise, each could function as the ALU of an individual core.

3/2/17 The Mk4 4th generation adder has been completed (in cleanup phase)! As you can see, I've set up 16 of the buggers side by side; they could be easily used in an SIMD setup of the scale of mark2222's GPU. Otherwise, each could function as the ALU of an individual core. -

QuanTech 19th Feb 2017

greetings.

greetings.